حتما اسم حافظه DDR به گوشت خورده، همون قطعاتی که به اسم رم (RAM) میشناسیم و توی کامپیوترها، لپتاپها و گوشیهای هوشمند ما پیدا میشن. نوع کممصرف این حافظهها که بهشون LPDDR (مخفف Low-power DDR) میگن، امروزه تقریبا توی هر دستگاهی از موبایل و اینترنت اشیا گرفته تا سرورها، کنسولهای بازی، رباتیک و حتی مراکز داده و هوش مصنوعی کاربرد دارن.

اخیرا انجمن JEDEC که استانداردهای این حوزه رو تعیین میکنه، مشخصات نسل جدید این حافظهها یعنی LPDDR6 رو منتشر کرده. این نسل جدید قراره سرعت انتقال اطلاعات رو به ۱۴.۴ گیگابیت بر ثانیه برسونه که تقریبا ۵۰ درصد از سریعترین نسخه نسل قبلی یعنی LPDDR5X بیشتره. ظرفیت این رمها هم میتونه بین ۴ تا ۶۴ گیگابایت باشه.

همزمان با این استاندارد، صحبت از نسل جدید رمهای دسکتاپ یعنی DDR6 هم هست. پیشبینی میشه که این رمها در سال ۲۰۲۶ برای تایید نهایی پلتفرمها آماده بشن، سال ۲۰۲۷ وارد مراکز داده بشن و حدود سال ۲۰۲۸ یا ۲۰۲۹ به کامپیوترهای خانگی برسن. رمهای DDR6 هم با سرعت پایه ۸۸۰۰ مگاترنسفر بر ثانیه (MT/s) شروع میشن و برنامهریزی شده که تا ۱۷۶۰۰ و حتی ۲۱۰۰۰ مگاترنسفر بر ثانیه هم برسن.

تغییرات ساختاری و فنی در نسل جدید

یکی از تغییرات مهم در LPDDR6 مربوط به معماری داخلیشه. هر دستگاه LPDDR6 دو «زیرکانال» داره که هر کدوم یک باس داده ۱۲ بیتی (x12) دارن. این یعنی عرض کل باس داده به ۲۴ بیت (x24) میرسه و LPDDR6 رو به اولین رم با عرض دادهای تبدیل میکنه که توانی از عدد ۲ نیست. البته انتقال داده واقعی هنوز ۳۲ بایت هست و بیتهای اضافه برای حمل فراداده (Metadata) استفاده میشن.

اینم یه نکته جدیده: برای اولین بار، فرادادههایی مثل کد تصحیح خطا (ECC) یا ماسک داده، به جای اینکه پینهای اختصاصی روی رم داشته باشن، مستقیما داخل بستههای داده قرار میگیرن. این کار پوشش قابلیت اطمینان، دسترسپذیری و سرویسدهی (RAS) رو بهتر میکنه؛ چیزی که طراحان سیستم مدتها دنبالش بودن.

برای رمهای دسکتاپ DDR6 هم معماری جدید ۴×۲۴ بیتی برای زیرکانالها در نظر گرفته شده که باعث افزایش شدید سرعت میشه ولی چالشهای جدیدی برای یکپارچگی سیگنال ایجاد میکنه. در حال حاضر رمها از مدولاسیون دامنه پالس (PAM) برای سیگنالدهی استفاده میکنن اما این روش با سرعتهای بالای DDR5 به محدودیت خورده. ممکنه JEDEC برای DDR6 به استاندارد NRZ روی بیاره، اما این موضوع هنوز نهایی نشده.

تمرکز ویژه روی امنیت و مصرف بهینه انرژی

امنیت و مصرف بهینه انرژی دوتا از مهمترین بخشهای استاندارد جدید LPDDR6 هستن.

- مقابله با حمله Row Hammer: یکی از چالشهای امنیتی بزرگ در رمها، مشکلی به اسم Row Hammer هست که میتونه باعث خرابی داده بشه. رمهای قدیمیتر مثل LPDDR5 یا DDR5 با مدیریت رفرش تا حدی با این مشکل مقابله میکردن. اما LPDDR6 اولین استانداردیه که یک راه حل مشخص داره: شمارش فعالسازی هر ردیف یا PRAC. در این روش هم میزبان (پردازنده) و هم خود رم، تعداد دفعاتی که یک ردیف فعال میشه رو میشمرن تا از فعالسازی بیش از حد و خرابی داده جلوگیری کنن. به گفته اسامو ناگاشیما، رئیس گروه کاری LPDDR در JEDEC، این ویژگی به همراه پاریتی فرمان و آدرس و کد تصحیح خطای داخلی (On-die ECC) محافظت خوبی برای یکپارچگی داده فراهم میکنه.

- بهینهسازی مصرف انرژی: در LPDDR6 نوآوریهای زیادی برای کاهش مصرف انرژی انجام شده:

- فرمانهای ورودی متناوب: دستورات فقط در سیکلهای زوج کلاک شروع میشن که به کاهش قابل توجه مصرف برق ورودی/خروجی کمک میکنه.

- گزینههای مقیاسپذیری ولتاژ و فرکانس (DVFS): این نسل از سه ریل ولتاژ مختلف پشتیبانی میکنه: بالا (DVFSH)، پایین (DVFSL) و VDD2D. این در حالیه که LPDDR5 فقط دو حالت بالا و پایین داشت.

- حالت بهرهوری (Efficiency Mode): این رمها میتونن از حالت بهرهوری استاتیک یا داینامیک برای کاهش مصرف برق ورودی/خروجی و دو برابر کردن ظرفیت دستگاه استفاده کنن.

- بهینهسازی رفرش: در LPDDR6، میزبان میتونه کنترل کنه که کدوم دو بانک حافظه رفرش بشن، به جای روش نوبتی که در نسلهای قبل بود. این به بهینهسازی زمانبندی کمک میکنه.

به گفته جفری چانگ، نایب رئیس کمیته فرعی JC-42.6 در JEDEC، بخش زیادی از مصرف انرژی مربوط به ارتباط بین رم و پردازنده هست و پهنتر کردن مسیر داده ولی با سرعت کمتر، اجازه میده از فرستنده و گیرندههایی با مصرف برق پایینتر استفاده بشه.

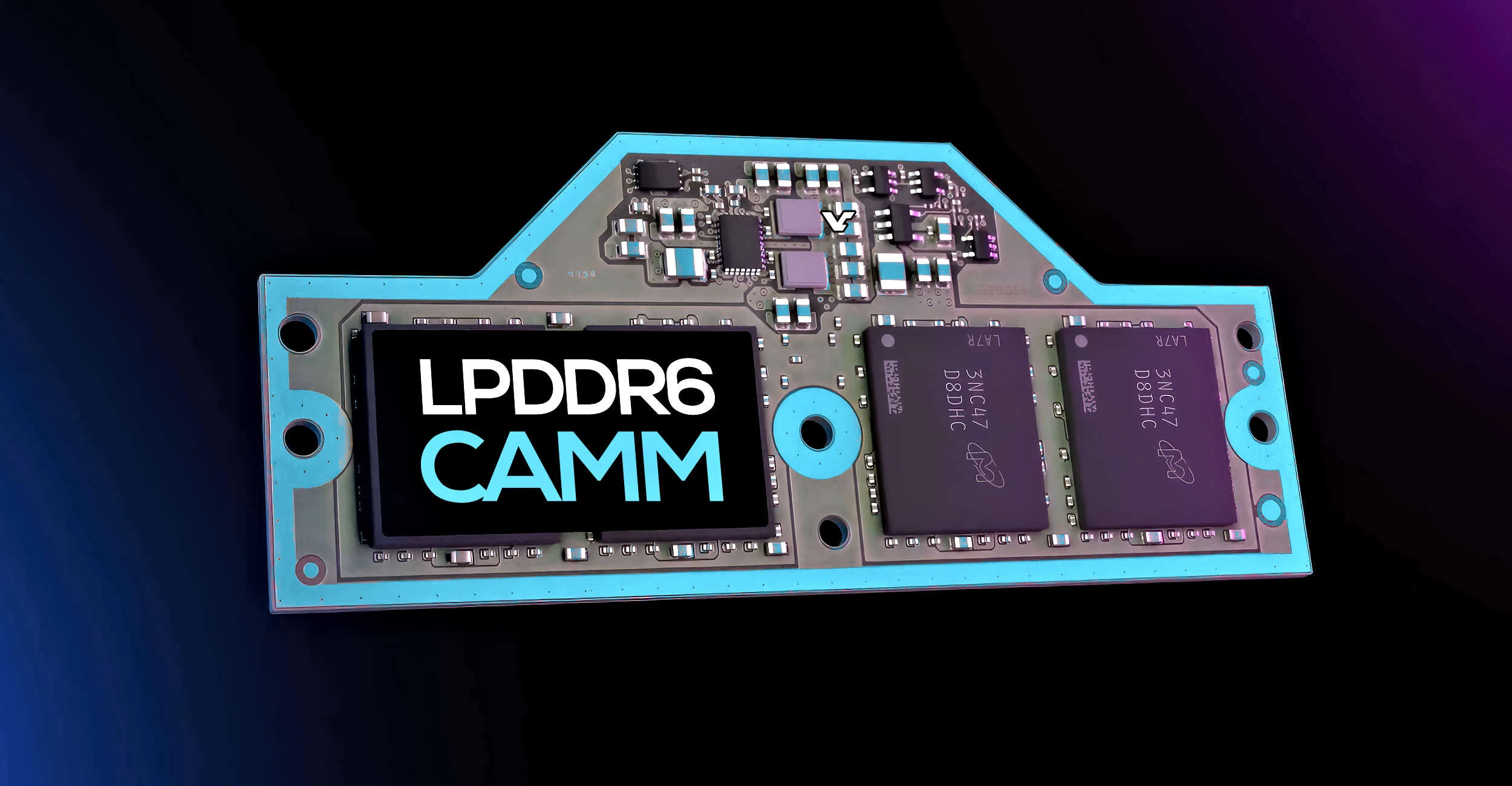

خداحافظی با ماژولهای DIMM و سلام به CAMM2

شاید بزرگترین تغییری که کاربران عادی با چشم میبینن، تغییر شکل فیزیکی ماژولهای رم باشه. JEDEC اعلام کرده که رمهای DDR6 و LPDDR6 از فرم فاکتور جدید CAMM2 استفاده خواهند کرد. در این طراحی جدید، ماژول رم به جای اینکه مثل رمهای DIMM و SO-DIMM امروزی به صورت عمودی روی مادربرد نصب بشه، به صورت موازی با مادربرد قرار میگیره.

دلیل این تغییر اینه که با بالا رفتن سرعت در DDR5، طراحی فعلی اسلاتهای رم روی مادربرد باعث مشکلات سیگنالدهی میشه. ماژول CAMM2 این مشکل رو با دو روش حل میکنه:

- اتصالات لحیمشده اسلاتهای DIMM که تداخل رادیویی ایجاد میکنن و میتونن تا ۴۰۰ مگاترنسفر بر ثانیه از سرعت رم کم کنن، حذف میشن.

- توپولوژی مسیر سیگنال به جای مادربرد، روی خود ماژول CAMM2 طراحی میشه که عملکرد بهتری داره.

البته گزینههای دیگهای هم مطرحه. ممکنه در لپتاپها و مینیپیسیها شاهد رمهای لحیمشده بیشتری باشیم. این کار امکان ارتقا رو از کاربر میگیره اما مشکلات سیگنالدهی رو در مرحله طراحی حل میکنه. دستگاههایی مثل پردازندههای Lunar Lake اینتل یا چیپهای سری M اپل نمونههایی از این رویکرد هستن.

قابلیت اطمینان، دسترسپذیری و سرویسدهی (RAS)

LPDDR6 ویژگیهای پیشرفتهای برای اطمینان از صحت دادهها داره:

- تشخیص و تصحیح خطا: این رمها از کد تصحیح خطای روی خود چیپ و لینک ارتباطی پشتیبانی میکنن که میتونه خطاهای تکبیتی رو تصحیح و خطاهای چندبیتی رو تشخیص بده. همچنین حالتی به اسم EDC وجود داره که پوشش تشخیص خطا رو به ۱۰۰ درصد میرسونه.

- پاکسازی خطا (Error Scrub): مثل DDR5، این رمها میتونن به صورت خودکار یا دستی دادهها رو بخونن، خطاها رو پیدا و تصحیح کنن و داده درست رو دوباره در حافظه بنویسن.

- گزارش خطا: برای اولین بار در خانواده LPDDR، این رمها چهار رجیستر خطا دارن که خطاهای جدی مثل مشکلات ECC یا PRAC رو به میزبان اطلاع میدن و یک سیگنال هشدار اختصاصی هم برای این کار دارن.

مقایسه LPDDR6 با LPDDR5/5X

با وجود همه ویژگیهای جدید، بعضی از قابلیتهای LPDDR5/5X در نسل جدید حذف شدن. جدول زیر خلاصهای از این تفاوتها رو نشون میده:

| ویژگی | LPDDR6 | LPDDR5/5X |

|---|---|---|

| پاریتی فرمان/آدرس (CA Parity) | بله | خیر |

| پین نوشتن ماسکشده/DMI | خیر | بله |

| رجیسترهای خطا/هشدار | بله | خیر |

| کپی داده/Write-X | خیر | بله |

| حالت carve-out برای فراداده | بله | خیر |

| کد تصحیح خطای داخلی (On-Die ECC) | بله | خیر |

| ریلهای ولتاژ | بالا/پایین/VDD2D | بالا/پایین |

| حالت خواب عمیق (Deep Sleep) | خیر | بله |

| کالیبراسیون ZQ | پسزمینه | پسزمینه/مبتنی بر فرمان |

| نسبت کلاک نوشتن به فرمان | ۲:۱ | ۲:۱ یا ۴:۱ |

| سازماندهی بانک | فقط گروه بانکی | گروه بانکی/۱۶ بانک/۸ بانک |

| مقابله با Row Hammer | PRAC | RFM, DRFM, ARFM |

دیدگاهتان را بنویسید